Get the job you really want.

Maximum of 25 job preferences reached.

Top Tech Jobs & Startup Jobs

Semiconductor

As an intern, you will design and develop AI tools to improve SSD testing processes, collaborate with cross-functional teams, and analyze test data to enhance efficiency.

Top Skills:

C++JavaMatplotlibPandasPythonPyTorchSeabornTensorFlow

Semiconductor

The Executive Assistant will provide operational support to business leaders, manage schedules, communications, travel arrangements, and handle confidential information, while ensuring a smooth workflow.

Top Skills:

ExcelMS OfficeOutlookPowerPointWord

Semiconductor

The role involves DSP design for high speed Serdes, requiring deep knowledge of digital design flow, high-speed interconnect architectures, and experience in RTL design and verification.

Top Skills:

Verilog-Hdl,System Verilog,Pam4,Pam6,Dsp,Pcie,100Gbps Ethernet,200Gbps Ethernet,Amba Bus,I2C,Spi,Uart

Semiconductor

The role involves developing Samsung Exynos AP software, diagnosing issues, customer support, and collaborating with cross-functional teams.

Top Skills:

Arm ArchitectureC/C++LinuxRtos

Semiconductor

Develop firmware for NVMe or SAS SSDs. Analyze and debug firmware issues, conduct OEM customization, and assist customers onsite. Requires strong C/C++ programming skills and experience with storage protocols.

Top Skills:

C,C++,Uart,Jtag,Ice,Sas,Sata,Scsi,Fc,Nvme,Pcie

New

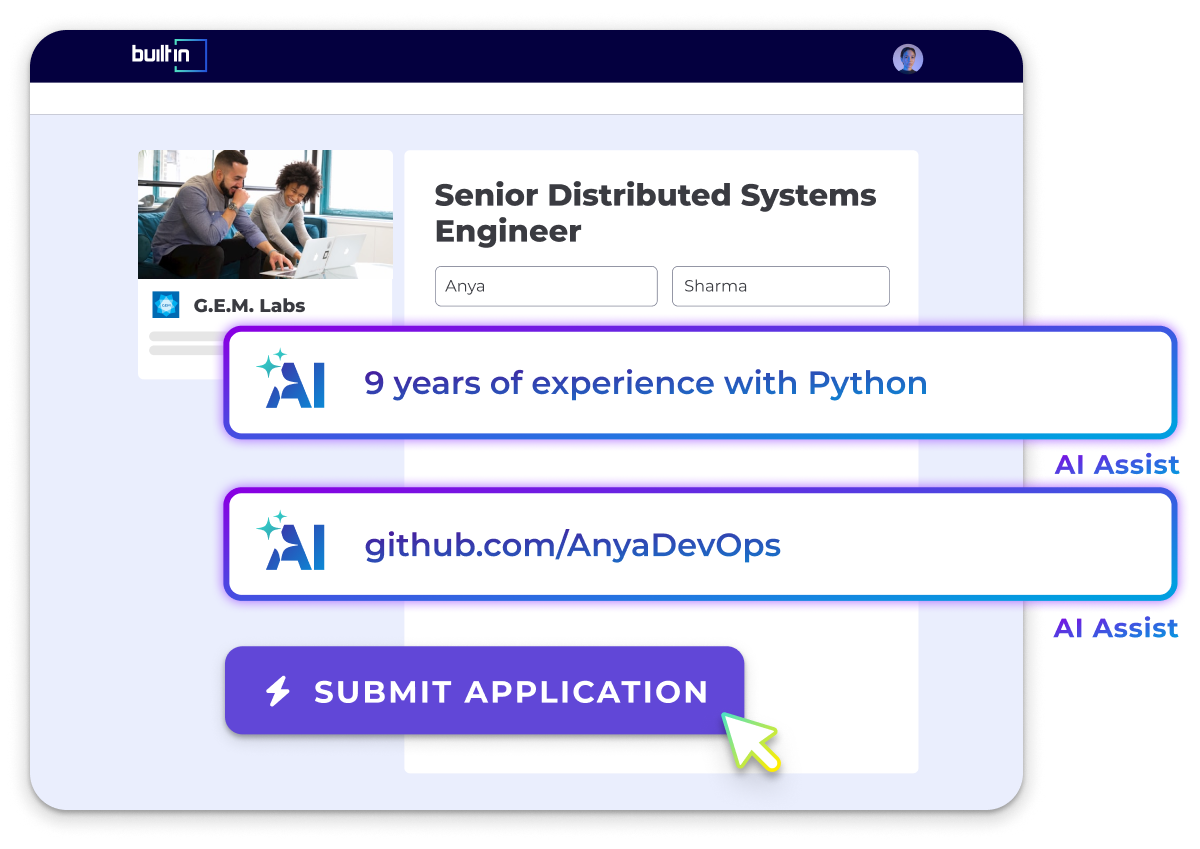

Cut your apply time in half.

Use ourAI Assistantto automatically fill your job applications.

Use For Free

Semiconductor

The Account Manager for Foundry Sales is responsible for developing and managing new accounts in the semiconductor industry, leading sales efforts, and collaborating with internal teams to meet customer needs and close deals effectively.

Top Skills:

Ip EcosystemSemiconductor Process TechnologySemiconductor Technologies

Semiconductor

The Director, Foundry Sales Account Manager will drive new account acquisitions, manage customer relationships, and collaborate with internal teams in the semiconductor industry, focusing on sales strategy and customer requirements.

Top Skills:

Contract NegotiationsMarketingSales StrategySemiconductor TechnologySupply Chain Management

Semiconductor

As an HR Business Partner, you will support organizational strategies, influence executives, and enhance employee relations, talent management, and performance management.

Top Skills:

ExcelMicrosoft PowerpointWorkday

Semiconductor

The Senior HR Business Partner will provide HR leadership, align initiatives with business strategies, and drive effectiveness through strategic and tactical HR practices. The role involves partnering with leaders, managing change initiatives, and fostering a high-performing workforce.

Semiconductor

Internship involves designing and implementing ML compilers, optimizing them for performance in deep learning on different hardware, and collaborating with teams to enhance compiler features.

Top Skills:

C++JaxLlvmMlirPyTorchTensorFlow

Top Tech Companies Hiring

See AllPopular Job Searches

Software Engineer Jobs

Aerospace Thermal Engineering Jobs

AI Engineer Jobs

Automation Engineer Jobs

Backend Developer Jobs

Blockchain Developer Jobs

Cloud Architect Jobs

Cloud Engineer Jobs

Design Engineer Jobs

DevOps Engineer Jobs

Director Of Engineering Jobs

Electrical Engineering Jobs

Embedded Software Engineer Jobs

Engineering Jobs

Engineering Manager Jobs

Environmental Engineering Jobs

Field Engineer Jobs

Full Stack Developer Jobs

Game Developer Jobs

Industrial Engineering Jobs

Machine Learning Engineer Jobs

Manufacturing Engineer Jobs

Mechanical Engineering Jobs

Network Engineer Jobs

Process Engineer Jobs

Project Engineer Jobs

Prompt Engineering Jobs

Robotics Engineer Jobs

Salesforce Administrator Jobs

SharePoint Developer Jobs

Site Reliability Engineer Jobs

Software Engineering Manager Jobs

Solutions Architect Jobs

SQL Developer Jobs

Structural Engineer Jobs

System Engineer Jobs

Test Engineer Jobs

Web Developer Jobs

Tech Jobs & Startup Jobs in Bangalore

Tech Jobs & Startup Jobs in Chennai

Tech Jobs & Startup Jobs in Delhi

Tech Jobs & Startup Jobs in Hyderabad

Tech Jobs & Startup Jobs in Kolkata

Tech Jobs & Startup Jobs in Mumbai

Tech Jobs & Startup Jobs in Pune

Tech Jobs & Startup Jobs in Belfast

Tech Jobs & Startup Jobs in Bristol

Tech Jobs & Startup Jobs in Dublin

Tech Jobs & Startup Jobs in Edinburgh

Tech Jobs & Startup Jobs in London

Tech Jobs & Startup Jobs in Manchester

Tech Jobs & Startup Jobs in Calgary

Tech Jobs & Startup Jobs in Ottawa

Tech Jobs & Startup Jobs in Toronto

Tech Jobs & Startup Jobs in Vancouver

Tech Jobs & Startup Jobs in Singapore

Tech Jobs & Startup Jobs in Melbourne

Technology Jobs & Startup Jobs in Sydney

Tech Jobs & Startup Jobs in Brazil

Tech Jobs & Startup Jobs in Czechia

Tech Jobs & Startup Jobs in France

Tech Jobs & Startup Jobs in Germany

Tech Jobs & Startup Jobs in Hungary

Tech Jobs & Startup Jobs in India

Tech Jobs & Startup Jobs in Israel

Tech Jobs & Startup Jobs in Italy

Tech Jobs & Startup Jobs in Japan

Tech Jobs & Startup Jobs in Malaysia

Tech Jobs & Startup Jobs in Mexico

Tech Jobs & Startup Jobs in Netherlands

Tech Jobs & Startup Jobs in New Zealand

Tech Jobs & Startup Jobs in Poland

Tech Jobs & Startup Jobs in Portugal

Tech Jobs & Startup Jobs in Romania

Tech Jobs & Startup Jobs in Spain

Tech Jobs & Startup Jobs in the Philippines

Tech Jobs & Startup Jobs in Turkey

Work your passion. Live your purpose.

Explore all your job opportunities on Built In.

Most Popular Searches

More Job Categories

Jobs by Expertise

Data + Analytics

Analytics Jobs

Analysis & Reporting Jobs

Business Intelligence Jobs

Data Engineering Jobs

Data Science Jobs

Machine Learning Jobs

Management Jobs

Other Jobs

Developer + Engineer

Android (Java) Jobs

C++ Jobs

C# Jobs

DevOps Jobs

Front-End Jobs

Golang Jobs

Java Jobs

Javascript Jobs

Hardware Jobs

iOS (Objective-C) Jobs

Linux Jobs

Management Jobs

.NET Jobs

Perl Jobs

PHP Jobs

Python Jobs

QA Jobs

Ruby Jobs

Salesforce Jobs

Sales Engineer Jobs

Scala Jobs

Other Jobs

Jobs by Location

Albuquerque, NM Jobs

Ann Arbor, MI Jobs

Atlanta, GA Jobs

Austin, TX Jobs

Baltimore, MD Jobs

Baton Rouge, LA Jobs

Birmingham, AL Jobs

Boise, ID Jobs

Boston, MA Jobs

Buffalo, NY Jobs

Charleston, SC Jobs

Charlotte, NC Jobs

Chicago, IL Jobs

Cincinnati, OH Jobs

Cleveland, OH Jobs

Colorado, CO Jobs

Columbus, OH Jobs

Dallas-Fort Worth, TX Jobs

Dayton, OH Jobs

Des Moines, IA Jobs

Detroit, MI Jobs

Fayetteville-Springdale-Rogers, Jobs

Greensboro, NC Jobs

Hampton Roads, VA Jobs

Hartford, CT Jobs

Houston, TX Jobs

Huntsville, AL Jobs

Indianapolis, IN Jobs

Jacksonville, FL Jobs

Kansas City, MO Jobs

Las Vegas, NV Jobs

Lexington, KY Jobs

Lincoln, NE Jobs

Little Rock, Jobs

Los Angeles, CA Jobs

Louisville, KY Jobs

Madison, WI Jobs

Memphis, TN Jobs

Miami, FL Jobs

Milwaukee, WI Jobs

Minneapolis–Saint Paul, MN Jobs

Nashville, TN Jobs

New Orleans, LA Jobs

New York City, NY Jobs

Ogden, UT Jobs

Oklahoma City, OK Jobs

Omaha, NE Jobs

Orlando, FL Jobs

Palm Bay-Melbourne-Titusville, Jobs

Pensacola, FL Jobs

Peoria, IL Jobs

Philadelphia, PA Jobs

Phoenix – Mesa – Scottsdale, AZ Jobs

Pittsburgh, PA Jobs

Portland, OR Jobs

Portland, ME Jobs

Providence, RI Jobs

Provo, UT Jobs

Raleigh-Durham, NC Jobs

Reno, NV Jobs

Richmond, VA Jobs

Rochester, NY Jobs

Sacramento, CA Jobs

Salt Lake City, UT Jobs

San Antonio, TX Jobs

San Diego, CA Jobs

San Francisco, CA Jobs

San Luis Obispo, CA Jobs

Santa Cruz, CA Jobs

Seattle, WA Jobs

Spokane, WA Jobs

St. Louis, MO Jobs

Tallahassee, FL Jobs

Tampa Bay, FL Jobs

Tucson, AZ Jobs

Tulsa, OK Jobs

Washington DC, Jobs

Wichita, KS Jobs

Wilmington, NC Jobs

All Filters

Total selected ()

No Results

No Results