Maximum of 25 job preferences reached.

Top Design Engineer Jobs

Aerospace • Automotive • Industrial • Manufacturing

The Product Design Engineer will design and develop innovative tools for orthopedic implants, prepare detailed drawings, and review test protocols while collaborating across departments.

Top Skills:

Solidworks

Agency • Information Technology • Professional Services • Manufacturing

The electrical designer creates complete electrical designs under guidance, applying theoretical knowledge, drafting plans, and coordinating with other disciplines.

Top Skills:

AutocadPhotometricRevitSpreadsheetWord Processing

Information Technology • Defense • Industrial • Manufacturing

The Design Engineer researches, designs, develops, tests, and supports electrical equipment for law enforcement, focusing on embedded systems for radar and lidar technologies.

Top Skills:

Circuit Design ToolsElectrical EngineeringEmbedded SystemsMultimetersNetwork AnalyzersOscilloscopesPcb Layout SoftwareSpectrum Analyzers

Artificial Intelligence • Cloud • Information Technology • Software

Drive performance verification and circuit quality signoff for CPU designs, evaluate new process nodes, and manage pre-to-post silicon correlation and debugging. Requires experience in circuit design and STA.

Top Skills:

Circuit DesignCpu DesignEngineeringTiming Analysis (Sta)

Artificial Intelligence

The Controls Integration Engineer will oversee the controls layer for Modular Data Centers, ensuring operability, integration, fault behavior, and documentation quality through design and testing oversight.

Top Skills:

BacnetModbus

Consumer Web • Food • Other • Appliances

Design, test, and implement improvements for refrigeration products; create 3D models and drawings; lead design changes; support manufacturing, reliability, and supply chain to deliver producible, cost-effective, and serviceable product improvements.

Top Skills:

3D ModelingCadCsaDraftingErpGd&TPlastic Part DesignPlmSheet Metal DesignSolidworksUl

Consumer Web • Food • Other • Appliances

Lead the design, validation, and implementation of embedded electromechanical systems for luxury appliances, collaborating with cross-functional teams to meet project deadlines and achieve performance targets.

Top Skills:

3D PrintingC++CadEmbedded SystemsPythonSolidworks

Biotech

Design and develop electronics for analytical instrumentation, focusing on low-noise signal measurement and high-voltage systems, collaborating with cross-functional teams.

Top Skills:

C/C++Hardware DebuggingPcb DesignPythonSchematic Capture

Manufacturing

The role involves developing embedded software, particularly for Android systems, managing design processes, collaborating with teams, and maintaining product quality through testing.

Top Skills:

Android SdkCC++Embedded SystemsJavaKotlin

Manufacturing

Drive mechanical system design and integration for marine products, ensuring manufacturability and compliance. Collaborate cross-functionally, mentor engineers, and validate designs using testing and regulations.

Top Skills:

CadFeaMS OfficeSolidworksTeamcenter

Industrial • Manufacturing

Design Engineer responsible for CAD design, tooling requirements, and manufacturing feasibility. Tasks include creating drawings, evaluating processes, and collaborating with teams.

Top Skills:

CadMS OfficeSolidworks

Information Technology • Software

Responsible for designing and verifying complex digital circuits, mentoring junior engineers, collaborating with other disciplines, and providing technical guidance.

Top Skills:

HyperlynxSiemens (Mentor) Dxdesigner

New

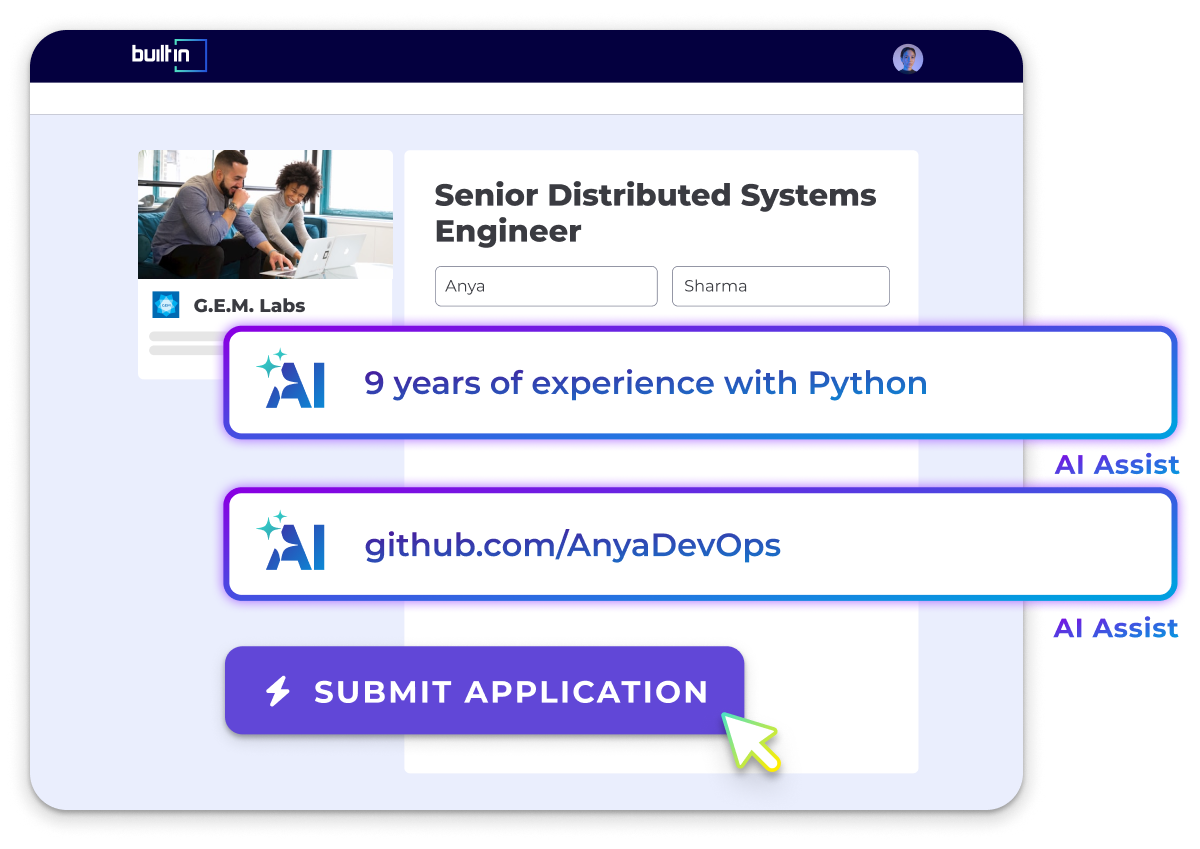

Cut your apply time in half.

Use ourAI Assistantto automatically fill your job applications.

Use For Free

Information Technology • Software

The Analog Design Engineer is responsible for designing complex analog circuits, verifying performance, and collaborating with cross-functional teams to enhance efficiencies and provide training.

Top Skills:

1553ArincDdrEthernetFpgaGpioHyperlynxI2CMicrocontrollerPcieSiemens Dx DesignerSpiUart

Software • Design

The Entry-Level Electrical Design Engineer assists in designing building systems, performs engineering calculations, creates construction documents, and supports project execution under senior engineers.

Top Skills:

AutocadBimRevit

Defense • Manufacturing

Design hardware for a propulsion system, own mechanical designs, manage vendors, validate designs, and conduct testing for satellite propulsion.

Top Skills:

CadFeaGd&TMechanical Design

Artificial Intelligence • Hardware • Machine Learning • Software

Lead design of high-speed analog/mixed-signal transceivers for silicon photonics systems. Drive block specifications with cross-functional teams, run post-layout and mixed-signal simulations, validate circuits in lab, define test plans, document designs, and mentor junior engineers.

Top Skills:

3D Em Simulation ToolsCmosFinfetMatlabMzmPythonRing ModulatorsSerdesSilicon PhotonicsSystemverilogTrans-Impedance Amplifier (Tia)Tx DriverVerilogams

Other • Professional Services • Real Estate • Energy

As an Electrical Design Engineer, you will design lighting and electrical systems, perform calculations, develop construction drawings, and manage client relationships while ensuring compliance with codes and standards.

Top Skills:

Agi32AutocadRevitSkm Power Systems

Artificial Intelligence • Machine Learning • Software

Design analog-mixed signal integrated circuits, optimize for low power performance, and collaborate on silicon bring up and debugging.

Top Skills:

CadenceSynopsis

Information Technology • Software

The Senior Photonic Circuits Design Engineer will design integrated photonic circuits, focusing on spectral filters and switches, leading R&D efforts in wireless optical communications.

Top Skills:

Commercial Layout Verification SoftwareDesign Rule ChecksGdsfactoryGitLayout Versus SchematicOptical Link ModelingOptical Link Simulation SoftwarePhotonic Device Simulation SoftwarePhotonic Integrated CircuitsPythonSpectral Filter Design

Software

The Senior Electronics Design Engineer will design and implement mixed signal circuits for MANET radios, perform testing and analysis, and collaborate with various teams to ensure high-quality electronics design.

Top Skills:

10Gb EthernetAltium DesignerAudio CodecsCFpgaHdi RoutingI2CMatlabPcb DesignPythonRs232SocUsb 3.0

Information Technology

Design and optimize RF switching and wideband linear amplifier circuits (sub-GHz to 10 GHz) with GaN emphasis. Use ADS/AWR for schematic, layout, verification; support modeling, PDK/parameter extraction, system-level analysis, DFT/DFM, packaging, and cross-team collaboration with device and systems engineers.

Top Skills:

Awr Microwave OfficeClass D Amplifier DesignCmos SwitchingGaasGanKeysight AdsMatlabPythonVerilog-A

Software • Semiconductor • Manufacturing

The Design Implementation Engineer will manage design implementation for ASIC/SoC, focusing on timing closure, physical verification, and adopting Broadcom's design methodologies. Expected to utilize tools for timing analysis, power optimization, and equivalent checks.

Top Skills:

CaliberIcc2InnovusLecPrimetimePrimetime

Software • Semiconductor • Manufacturing

The IC Design Engineer designs and develops integrated circuits, oversees ASIC development, defines architecture, and evaluates processes. Responsibilities include leading product delivery and mentoring junior team members.

Top Skills:

AsicLogic DesignSystem Simulation

Software • Semiconductor • Manufacturing

Design and develop high-speed analog circuits for electronic systems, conduct tests, analyze data, and select reliable components.

Top Skills:

Cad ToolsHigh-Speed Analog Circuit Design

Hardware • Manufacturing

The Principal Digital Design Engineer will develop digital microarchitecture for FPGAs, focusing on logic design, verification, and collaboration across teams to ensure system specifications are met.

Top Skills:

FpgaSystemverilogVerilog

Let Your Resume Do The Work

Upload your resume to be matched with jobs you're a great fit for.

Success! We'll use this to further personalize your experience.

Top Companies Hiring Design Engineers

See AllPopular Job Searches

All Software Engineer Jobs

.NET Developer Jobs

Aerospace Thermal Engineering Jobs

AI Engineer Jobs

Android Developer Jobs

Automation Engineer Jobs

Backend Developer Jobs

Blockchain Developer Jobs

C# Jobs

C++ Jobs

Cloud Architect Jobs

Cloud Engineer Jobs

Design Engineer Jobs

DevOps Engineer Jobs

Director Of Engineering Jobs

Electrical Engineering Jobs

Embedded Software Engineer Jobs

Engineering Jobs

Engineering Manager Jobs

Environmental Engineering Jobs

Field Engineer Jobs

Front End Developer Jobs

Full Stack Developer Jobs

Game Developer Jobs

Golang Jobs

Hardware Engineer Jobs

Industrial Engineering Jobs

iOS Developer Jobs

Java Developer Jobs

Javascript Developer Jobs

Linux Jobs

Manufacturing Engineer Jobs

Mechanical Engineering Jobs

Network Engineer Jobs

PHP Developer Jobs

Process Engineer Jobs

Project Engineer Jobs

Prompt Engineering Jobs

Python Jobs

QA Jobs

Robotics Engineer Jobs

Ruby on Rails Jobs

Salesforce Administrator Jobs

Salesforce Developer Jobs

Scala Jobs

Sharepoint Developer Jobs

Site Reliability Engineer Jobs

Software Engineering Manager Jobs

Solutions Architect Jobs

SQL Developer Jobs

Structural Engineer Jobs

System Engineer Jobs

Test Engineer Jobs

Web Developer Jobs

All Filters

Total selected ()

No Results

No Results