Maximum of 25 job preferences reached.

Top Design Engineer Jobs

Artificial Intelligence • Cloud • Information Technology • Software

As a Senior RTL Design Engineer, you'll develop next-gen microprocessors, optimize CPU architecture and microarchitecture, and provide technical leadership in design processes.

Top Skills:

PerlPythonSystem VerilogTclVerilog

Industrial • Manufacturing

The Electrical Design Engineer designs electrical wire harness systems, works on configurations, integrations, and troubleshooting for off-highway equipment, collaborating with teams for product development.

Top Skills:

Capital HarnessCreoPdmlinkProcableWindchill

3D Printing

Design and develop hermetic/ceramic/metal packages for aerospace and high reliability applications, working with suppliers and developing technical expertise.

Top Skills:

AutocadExcelPowerPointWord

Hardware • Manufacturing

The role involves full-custom layout of mixed-signal ICs, focusing on performance and integration into SoCs using advanced FinFET processes.

Top Skills:

Cadence VirtuosoPythonSiemens CalibreSkillSynopsys Custom CompilerSynopsys IcvTcl

Aerospace

The role involves designing mechanical systems compliant with codes, conducting engineering calculations, mentoring junior engineers, and overseeing compliance for pressure vessels and piping systems.

Top Skills:

CatiaFea ToolsGd&TNxSolidworks

Cloud

The Design Engineer I provides technical expertise in network technologies, assists customers with design solutions, prepares configurations, and creates technical content for sales.

Top Skills:

Centralized Cloud ManagementRoutingSwitching L2/L3Wireless

25 Days AgoSaved

Industrial • Manufacturing

Design and develop suspension, steering, and braking components for off-road vehicles, managing the entire product lifecycle from concept to manufacturing.

Top Skills:

3D CadCreoFinite Element Analysis (Fea)Ptc Windchill

Energy • Utilities

The Engineer - Electric Substation Design is responsible for managing design work and project construction for electric substations, ensuring safety and compliance with corporate procedures while working collaboratively with teams.

Top Skills:

Electric SubstationsEngineeringProject Management

Software • Semiconductor • Manufacturing

Responsible for physical design of chips, floorplanning, PnR, timing closure, physical verification, and automation of design flow using scripting languages.

Top Skills:

GdsiiIc DesignIr/Em AnalysisMentor CalibrePerlPnrPythonTcl

Logistics

The Design Engineer will design layouts, create proposals, and manage material orders for engineered solutions in material handling.

Top Skills:

AutocadMS Office

Artificial Intelligence • Machine Learning • Software

Lead the layout design for high-complexity AI accelerator cards, manage constraints across designs, and drive automation for PCB layouts ensuring the highest signal integrity and efficient power delivery.

Top Skills:

Cadence AllegroPythonSkillTcl

Greentech • Renewable Energy

The Senior Control System Integration and Design Engineer will design, configure, and program ICS/OT systems and supervise control system commissioning. Responsibilities include SCADA/HMI design, networking, cybersecurity enforcement, and mentoring junior team members.

Top Skills:

CybersecurityHmiIcsNetworkingOtProgrammable Logic ControllersScada

New

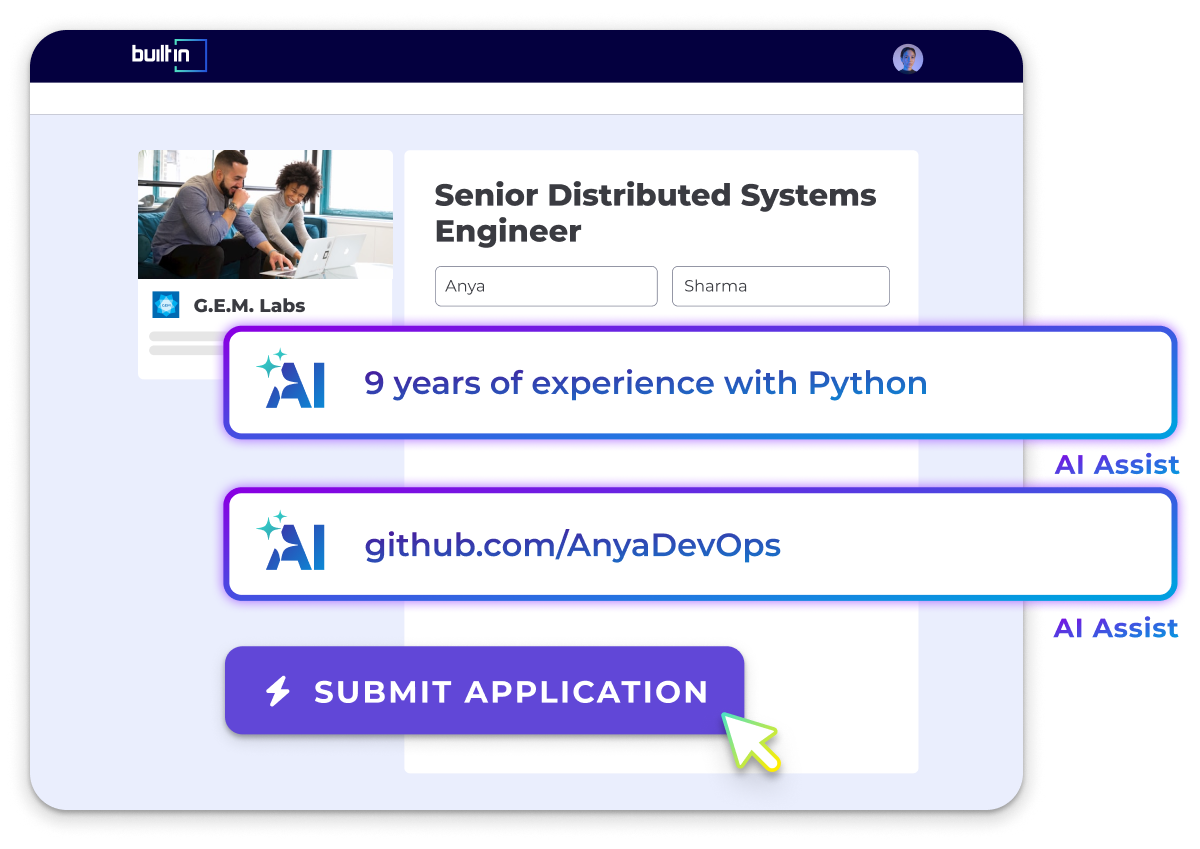

Cut your apply time in half.

Use ourAI Assistantto automatically fill your job applications.

Use For Free

Artificial Intelligence • Cloud • Information Technology • Software

Design critical foundational collateral for Intel's advanced technology in analog/RF circuit design, ensuring quality and efficiency in product development.

Top Skills:

Cadence VirtuosoMatlabPythonSpice

Artificial Intelligence • Cloud • Information Technology • Software

Design and develop custom digital circuits for Intel CPUs, focusing on optimization and collaboration with cross-functional teams to enhance CPU technology.

Top Skills:

Cmos Circuit DesignDigital Logic OptimizationsEbb Design ToolsMemory DesignVlsi Circuits

Industrial • Manufacturing

The role involves designing silicon photonic integrated circuits, validating designs, supporting tapeouts, and collaborating with cross-functional teams for product development.

Top Skills:

AdsCadence VirtuosoCst Microwave StudioHfssLumericalSynopsys OptocompilerTidy3D

Information Technology • Software

Responsible for developing and supporting responsive web applications, collaborating on larger features and independently managing smaller tasks while writing clean code.

Top Skills:

.Net WebapiAngularjsAWSCSSGCPGruntGulpHTML5JavaScriptPythonSassSQL

Information Technology • Software

Architect and develop responsive web applications for internal users. Requires significant experience in game design and technical proficiency in various programming languages.

Top Skills:

.NetC#C++HololensHtc ViveJavaScriptPythonRestful ApisUnityUnreal

Information Technology • Software

The Design Quality Engineer ensures compliance with quality regulations in the medical device industry, focusing on risk management, design verification, and validation processes.

Top Skills:

Fda RequirementsGlpGmpIso ProceduresMddQsr

Information Technology • Software

Oversee software quality in medical device development, ensuring adherence to regulations, risk management, and mentoring design teams.

Top Skills:

Agile Software DevelopmentCC++Fda Quality System RegulationIec 62304Iso 13485

Reposted 2 Days AgoSaved

Energy • Renewable Energy

Lead the design and analysis of mechanical systems and components for a fusion energy power plant, ensuring longevity in extreme conditions. Mentor engineers and support design reviews while optimizing materials and design choices through analysis.

Top Skills:

AbaqusAnsysC++CadFortranPython

Professional Services

Seeking an OpenRoads Project Engineer to develop 3D roadway designs, mentor junior engineers, collaborate on projects, and conduct design reviews. Requires 8 years experience in transportation engineering.

Top Skills:

AutocadBentley OpenroadsCivil 3DMS OfficeMicrostation

Reposted 2 Days AgoSaved

Healthtech • Other • Biotech

Provides quality engineering support for product design transfer in compliance with quality standards, coordinating risk management and conducting audits while mentoring team members.

Top Skills:

21 Cfr 820Iso 13485Iso 14791JmpLean ManufacturingMinitabOracleQuality Control ToolsSix SigmaStatistical Methodologies

Software • Semiconductor • Manufacturing

The Design Verification Engineer will verify cutting edge network switch routing designs, develop test plans, and execute verification processes for ASICs in networking applications.

Top Skills:

Object Oriented Programming (Oop)PerlPythonSystemverilogUvmVerilog

Software • Semiconductor • Manufacturing

Responsible for verification of networking ASICs, including developing test plans, environments, and executing verification processes using SystemVerilog. Requires strong experience in digital design and verification techniques.

Top Skills:

Object Oriented Programming (Oop)PerlPythonSystemverilogUvmVerilog

Aerospace • Information Technology • Software • Biotech • Design

The Design and Release Engineer will develop vehicle components from concept to production, focusing on 3D design, validation, feasibility, quality documentation, and project management.

Top Skills:

3Dx CadCaeGd&TPlm Systems

Let Your Resume Do The Work

Upload your resume to be matched with jobs you're a great fit for.

Success! We'll use this to further personalize your experience.

Top Companies Hiring Design Engineers

See AllPopular Job Searches

All Software Engineer Jobs

.NET Developer Jobs

Aerospace Thermal Engineering Jobs

AI Engineer Jobs

Android Developer Jobs

Automation Engineer Jobs

Backend Developer Jobs

Blockchain Developer Jobs

C# Jobs

C++ Jobs

Cloud Architect Jobs

Cloud Engineer Jobs

Design Engineer Jobs

DevOps Engineer Jobs

Director Of Engineering Jobs

Electrical Engineering Jobs

Embedded Software Engineer Jobs

Engineering Jobs

Engineering Manager Jobs

Environmental Engineering Jobs

Field Engineer Jobs

Front End Developer Jobs

Full Stack Developer Jobs

Game Developer Jobs

Golang Jobs

Hardware Engineer Jobs

Industrial Engineering Jobs

iOS Developer Jobs

Java Developer Jobs

Javascript Developer Jobs

Linux Jobs

Manufacturing Engineer Jobs

Mechanical Engineering Jobs

Network Engineer Jobs

PHP Developer Jobs

Process Engineer Jobs

Project Engineer Jobs

Prompt Engineering Jobs

Python Jobs

QA Jobs

Robotics Engineer Jobs

Ruby on Rails Jobs

Salesforce Administrator Jobs

Salesforce Developer Jobs

Scala Jobs

Sharepoint Developer Jobs

Site Reliability Engineer Jobs

Software Engineering Manager Jobs

Solutions Architect Jobs

SQL Developer Jobs

Structural Engineer Jobs

System Engineer Jobs

Test Engineer Jobs

Web Developer Jobs

All Filters

Total selected ()

No Results

No Results