Maximum of 25 job preferences reached.

Top Design Engineer Jobs

Biotech • Pharmaceutical

The Transducer Design Engineer will design ultrasound arrays, develop fabrication methods, and measure properties of elements while collaborating with other engineers.

Top Skills:

Acoustoelectric ModelingElectrical EngineeringMaterials ScienceUltrasound

Information Technology • Software

The Board Design Engineer will design complex high-speed PCBs, manage vendors, ensure signal integrity, and collaborate across teams, leveraging system knowledge.

Top Skills:

Cadence VirtuosoHigh-Speed Digital DesignPcb DesignSiemens Mentor Calibre

Automotive • Cloud • Software • Industrial • Manufacturing

The role involves designing analog and mixed-signal ICs for automotive power management, overseeing product development, and mentoring junior engineers.

Top Skills:

BicmosDmos

Automotive • Cloud • Software • Industrial • Manufacturing

This role involves designing analog and mixed-signal ICs for Power Management Products, circuit synthesis, and supporting design and testing efforts.

Top Skills:

Analog CircuitsBicmosDmosMixed-Signal Ics

Greentech • Other

The Design Engineer will perform structural analysis and design of prestressed concrete poles, ensuring manufacturability, supporting customer specifications, and providing solutions to design challenges.

Top Skills:

3D CadFinite Element MethodsMS Office

Artificial Intelligence • Information Technology • Software • Cybersecurity

Design and engineer a scalable gamified data collection platform by creating design systems and complex user interfaces, while enhancing developer tooling.

Top Skills:

Browser ExtensionsGamificationUi/Ux DesignVs Code

Artificial Intelligence • Payments • Software • Hospitality

As a Design Engineer, you'll build product and internal tools, prototype new features, and define UI architecture while collaborating closely with the team.

Top Skills:

CSSFigmaReactTailwindTypescript

Information Technology • Business Intelligence • Consulting • Defense

The Hardware Design Engineer designs integrated circuits and hardware components, conducts reverse engineering, and leads design efforts while guiding less experienced engineers.

Top Skills:

AsicDigital Signal ProcessorsFirmwareFpga

Healthtech

The Senior Design Engineer develops surgical instruments, creates designs using SolidWorks, drafts documentation, and collaborates on product development teams.

Top Skills:

3D Cad SoftwareSolidworks

Artificial Intelligence • Information Technology • Software • Consulting

The Physical Design Engineer will handle floor planning, P&R, timing closure, power planning, and physical verification for complex designs, ensuring high quality and adherence to specifications.

Top Skills:

JavaLintMaximoPtsiSynopsys DcSynopsys PcVerilogVhdl

Artificial Intelligence • Logistics • Software • Transportation • Automation

The Senior Design Engineer is responsible for 3D modeling, drafting, and detailed analysis of equipment designs, ensuring quality product delivery and project documentation.

Top Skills:

AutocadMS OfficeSolidworks

Aerospace

Lead development of airframe structure, ensuring compliance with FAA regulations, while mentoring engineers and optimizing design for manufacturing.

Top Skills:

CatiaCreoNxPdm SystemsSolidworks

New

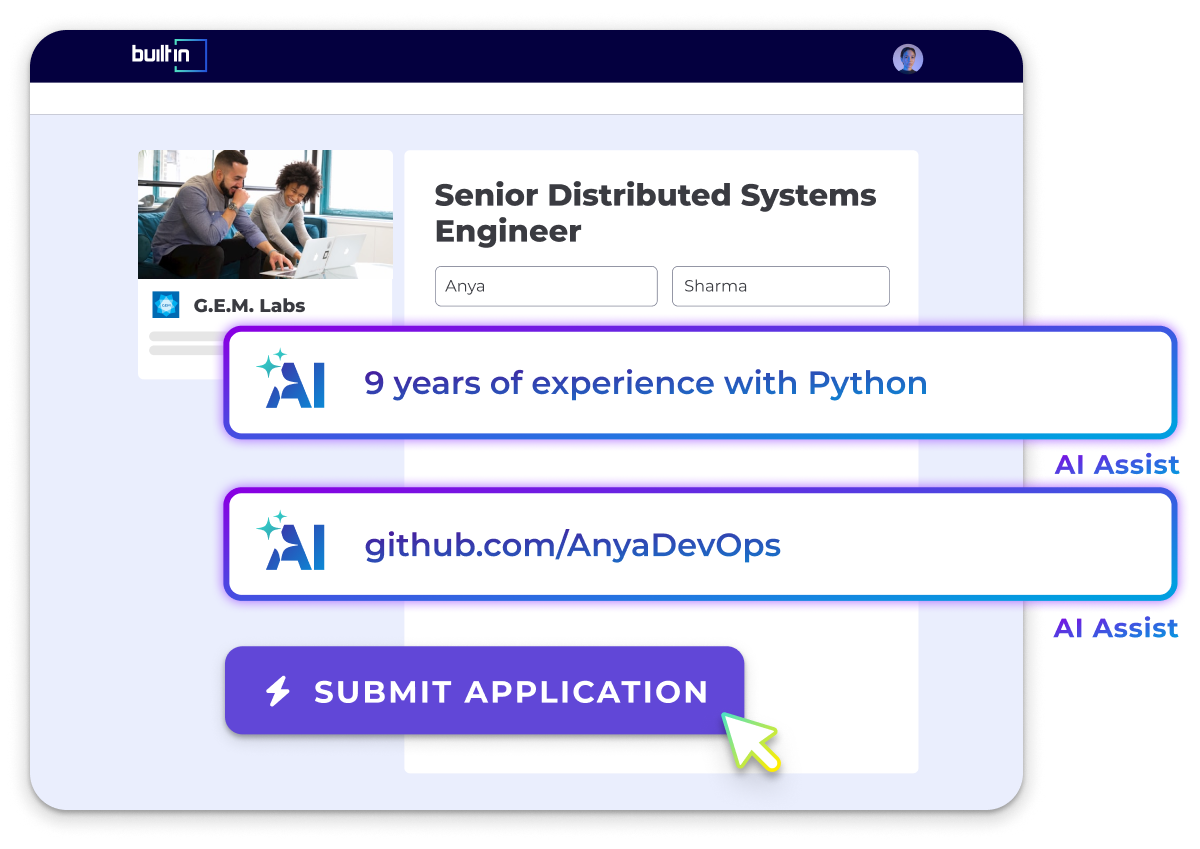

Cut your apply time in half.

Use ourAI Assistantto automatically fill your job applications.

Use For Free

Industrial • Manufacturing

Design, model, and validate new trailer products and components using CAE tools (Siemens NX, ANSYS). Collaborate with sales, operations, supply chain, and vendors to produce BOMs, ECRs/ECNs, prototypes, and cost-saving solutions while supporting manufacturing and warranty analysis.

Top Skills:

AnsysCaeDotEpicor ErpFmvssKaizenLean Six SigmaMS OfficeNhtsaSaeSiemens NxVa/Ve

Hardware

Design, simulate, and optimize metasurfaces for products, collaborate with engineering teams, automate tasks using simulation programming, and document methodologies.

Top Skills:

BpmFdtdFemGitJuliaMatlabPythonRcwaSlurmTmm

Artificial Intelligence • Automotive • Semiconductor

Design and layout very large-scale silicon photonic ICs (PICs) from floor-planning to back-end verification. Collaborate with analog, digital and packaging teams to meet opto-electronic, SI and PI requirements. Optimize and extend layout automation and verification flows using scripting and EDA tools to deliver production-ready PICs.

Top Skills:

CadenceCalibreDrcErcKlayoutLvsPegasusPythonSiemens MentorSilicon Photonics Process Design KitsSkillTsmc

Hardware

The Systems Design Engineer will develop advanced laser sources, focusing on cavity design, optics, and conversion efficiency models, requiring hands-on skills and analytical techniques.

Top Skills:

Laser DesignMatlabOptical Parametric OscillatorsOpticsPythonZemax

Hardware

Electrical Design Engineers at KLA work on PCB and system design, collaborating with mechanical engineers and firmware teams, while creating schematics and designs for electronic components.

Top Skills:

Ac Power DistributionAdsAltiumEagleHyperlynxOrcad PcbPadsProgrammable Logic Controllers

Energy

The Senior Mechanical Design Engineer will design critical hardware for fast reactors, ensuring compliance and collaboration with cross-functional teams on detailed designs and fabrication readiness.

Top Skills:

CatiaSiemens NxSiemens TeamcenterSolidworksSolidworks PdmWindchill

Hardware • Information Technology • Energy • Design • Utilities • Industrial • Renewable Energy

As an Electrical Systems Design Engineer, you will ensure accuracy in electrical project documentation, collaborate on schematic reviews and compliance with NEC, manage multiple projects, and support production with design assistance.

Top Skills:

BluebeamEpicorMicrosoft Office Suite

Industrial • Manufacturing

The Electrical Design Engineer will design and route electrical harnesses, develop schematics, collaborate with teams, ensure compliance, and support prototype builds.

Top Skills:

3D Cad SoftwareCapital HarnessCreo HarnessPlm SystemsTeamcenterWindchillZuken E3

Big Data • Information Technology

The Principal Digital Design Engineer will architect and implement advanced digital designs for AI connectivity, manage complex design blocks, and drive RTL implementations, ensuring production-quality silicon for high-speed protocols.

Top Skills:

CadenceCxlEthernetNvlinkPcieSynopsysUalink

Industrial • Manufacturing

The Design Engineer will develop high-performance equipment designs, ensure compliance with standards, prepare technical documentation, and manage project schedules while optimizing manufacturing processes.

Top Skills:

Engineering Software ToolsMS Office

Aerospace

The Motor Design Engineer will lead the design and development of cryogenic electric motors for lunar landers, focusing on performance analysis, electromagnetic design, and collaboration with teams for high-reliability components.

Top Skills:

Cad (Creo)Electromagnetic Simulation ToolsFea Analysis (Ansys)MatlabPlm SystemsPython

Aerospace • Other

As a Harnessing Design Engineer at SpaceX, you'll develop harness designs for Starlink satellites, manage trade studies, conduct testing, and collaborate with production teams.

Top Skills:

CadFeaNx CadTeamcenter

Energy • Renewable Energy

The Mechanical Design Engineer II will develop new products, provide documentation for components, optimize designs, support existing products, and ensure compliance with quality metrics.

Top Skills:

PdmSolidworks

Let Your Resume Do The Work

Upload your resume to be matched with jobs you're a great fit for.

Success! We'll use this to further personalize your experience.

Top Companies Hiring Design Engineers

See AllPopular Job Searches

All Software Engineer Jobs

.NET Developer Jobs

Aerospace Thermal Engineering Jobs

AI Engineer Jobs

Android Developer Jobs

Automation Engineer Jobs

Backend Developer Jobs

Blockchain Developer Jobs

C# Jobs

C++ Jobs

Cloud Architect Jobs

Cloud Engineer Jobs

Design Engineer Jobs

DevOps Engineer Jobs

Director Of Engineering Jobs

Electrical Engineering Jobs

Embedded Software Engineer Jobs

Engineering Jobs

Engineering Manager Jobs

Environmental Engineering Jobs

Field Engineer Jobs

Front End Developer Jobs

Full Stack Developer Jobs

Game Developer Jobs

Golang Jobs

Hardware Engineer Jobs

Industrial Engineering Jobs

iOS Developer Jobs

Java Developer Jobs

Javascript Developer Jobs

Linux Jobs

Manufacturing Engineer Jobs

Mechanical Engineering Jobs

Network Engineer Jobs

PHP Developer Jobs

Process Engineer Jobs

Project Engineer Jobs

Prompt Engineering Jobs

Python Jobs

QA Jobs

Robotics Engineer Jobs

Ruby on Rails Jobs

Salesforce Administrator Jobs

Salesforce Developer Jobs

Scala Jobs

Sharepoint Developer Jobs

Site Reliability Engineer Jobs

Software Engineering Manager Jobs

Solutions Architect Jobs

SQL Developer Jobs

Structural Engineer Jobs

System Engineer Jobs

Test Engineer Jobs

Web Developer Jobs

All Filters

Total selected ()

No Results

No Results